VHDLによるロジック設計(1)

これまで述べてきたのロジック回路シミュレータとアナログ回路シミュレータは、回路図を作成してシミュレーションする方法が取られてきた。これに対して、回路図を書かないでハードウェアの設計ができるハードウェア記述言語(HDL:Hardware Description Language)が高速の大規模ASICだけでなくCPLDやFPGAなどのプログラマブルロジックの設計にも使われはじめている。回路図を書かなくてもASICが設計できるという考えは、古い回路エンジニアにはなじみにくいと思われるが、PLDの開発用ソフトとして使われてきたPALASM、ABELやCUPLも広い意味でHDLと考えることができよう。ここではパソコンで利用できる低価格のHDL開発ツールの中からサイプレス社のWarp2とアコレード社のPeakVHDLを取り上げ、初歩的なHDLの文法と関連させながら、これらの開発ツールを利用したHDL設計の手法を学習する。

HDLの動向

今日、CPLD やFPGA の集積密度は急速に増加しており、デザイナーはシミュレーションと論理合成の標準的な設計言語であるHDLへの移行を余儀なくされている。現在、10万人のプログラマブルロジックのデザイナーのうち HDLを利用しているものはわずか10%程度と推定されている。したがって、言語ベースの論理合成ツールはプログラマブルロジックやASIC分野に今後急速に普及するものと考えられる。そして、これらの設計のために、より安価で、BasicやC言語と同じような感覚で簡単に習得できる本格的デザイン能力を持つ開発ツールが待望されている。

HDLの歴史とその特徴

現在、HDLの二大勢力はVHDLとVerilog-HDLで、事実上の標準となっている。米国Cadence Design System社によって開発されたHDLであるVerilog-HDLに対し、後発のVHDLは米国防総省のVHSIC(超高速集積回路)プロジェクトから生まれた。1986年にIEEEでHDLの基本言語として採用され公開された後、1987年にIEEE1076標準として正式承認された。さらに1993年に上位互換のVHDLであるIEEE 1164標準が採択され、電子産業界に広く普及してきた。

このようなVHDLは、HDLそれ自身の特徴をさらに高めたものとなっている。

・これまでの言語に比べ、抽象性が高い。

・トップダウン設計による階層設計が可能である。

・テストパターンもVHDLで記述し、回路シミュレーションが容易にできる。プロジェクトをシミュレートするためには、テストベンチと呼ばれるもう一つのVHDLプログラムを開発する必要がある。テストベンチは、シミュレーション中は階層設計の最上位にあり、シミュレータには、テストされる設計部分とテストベンチそのものの間には境界がなく、巨大なオートテスターのようなものと考えることができる。

・VHDLは標準言語としてIEEEで制定されており、VHDLで記述しておけばメーカーに依存しないので移植性が高い。また、開発ソフトが変わっても、デバイスが変わっても設計資産として生き残り、無駄にならない。

・VHDLからは論理合成ソフトにより、回路図をコンピュータに作らせることができる。

VHDLの開発ツールと学習教材

これまでHDL開発ツールはワークステーション用を中心としたもので学習曲線が長くその価格も高いため、デザイナーはVHDLへの移行を阻まれてきた。しかし、Windows95の登場を契機として、パソコンで利用できる低価格なものが各社から登場し、HDLによる設計はより身近なものとなってきた。

ここではパソコンベースのWindows95環境下で動作する低価格のVHDL開発ツールと学習教材について最近の2、3の例を紹介する。

(1)Accolade(アコレード)社

アコレード社のVHDLコンパイラーPeakVHDL(Version1)の評価版は、CQ出版社の「Desin Wave Magazine」創刊2号に付録のCDーROMとして添付された。最新バージョンはアコレード社のホームページ(http://www.accolade.com/)から、ダウンロードすることができる。容量は8MBあるのでかなりの時間がかかる。また、同ホームページにはVHDLの学習用教材として最適な"VHDL Made Easy!"が紹介されている。これは400ページにおよぶVHDLの学習用の書籍とCD-ROMがパッケージになっており、CDーROMにはVHDLコンパイラーPeakVHDLの評価版、マニュアル、サンプルのvhdファイルなどが収録されている。価格はUS$59.45と日本からの注文ではUS$22.50の航空便による送料がかかる。"VHDL Made Easy!"の注文は、注文書にビザかマスターカードのカード番号と有効日、発送先とメールアドレスなどを記入してパソコンFaxなどで送信すればよい。国際電話なので、頭に001と米国の国識別番号である1を加えて、001-1-425-788-3768のようにFAX番号を入力して送信する。ついこのあいだまで、0051を呼び出して米国のFAX番号を告げて接続していてもらっていたような気もするが嘘のような手軽さだ。筆者の場合、翌日には品物を発送したというEmailが入り、4、5日で注文品が届いた。パソコンとインターネットに感謝!。

(2)サイプレス社

米国サイプレス社のVHDL開発ツールWarp2は、「トランジスタ技術」誌(98年12月号)にも紹介されており、国内代理店(トーメン、富士エレクトロニクス、リョウヨウ)に申し込めば入手できる。これにも'VHDL for PROGRAMMABLE LOGIC'というタイトルの400ページの書籍が同梱されている。CDーROMにはエディタとコンパイラー機能を持つGalaxyとファンクション・シミュレータのNovaの他に、オンラインマニュアルとして288ページのユーザーズ・マニュアルと277ページ のリファレンス・マニュアルが収録されており、AcrobatReaderで読むことができる。

なお、前述のトランジスタ技術誌に掲載された記事のソースファイルははNiftyServeのFDEVICEのデータライブラリ#7からダウンロードできる。また米国サイプレスのホームページ(http://www.cypress.com/)にもVHDLトレーニング用ファイルやアップデート情報など有益な情報が多い。CPLDなどの製品情報も簡単に入手できるのでハンドブックが手元にない場合とかデータが古い場合など大いに重宝する。

(3)その他

MINC社は、'97年 7月に、学習が容易で、簡単に使える495ドルの強力なVHDL 合成ツール"VHDL Easy "を発表した。この製品はWindows'95とWindows NTプラットホーム上で動作し、PLDのデザインで、VHDL が有利であることを設計者に容易に納得させ得るものである。製品のアップデートとサポートはホームページ(http://www.minc.com )でオンラインサービスされている。

ViewLogic社のホームページ(http://www.viewlogic.com/)からWorkview Officeの評価版CDーROMの申し込みができる。

Warp2によるVHDL設計手順

初めに、Warp2に添付されているExampleの中から単純なVHDLのファイルを使ってWarp2によるCPLD設計の流れを手順を追って見てみよう。ここではインストールが済んでいる状態からスタートする。

手順1 c:にデレクトリvhdlbookをつくり、c:/warp/examples/vhdlbookの内容をコピー する。

手順2 スタート→プログラム→Warp R4と辿ってGalaxyを立ち上げる。

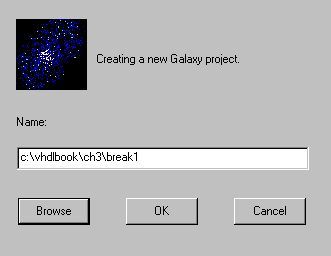

手順3 ProjectメニューでNewをクリックするとNewProjectダイヤログが開くのでc:/vhdlbook/ch3/break1と入力する(図1)とProjectウインドウが開く。

図1 New

Projectダイヤログ

図1 New

Projectダイヤログ 手順4 FileメニューからAddAllを選択するとファイル名がファイルリストに表示されるのでdataflow.vhdを選択する。

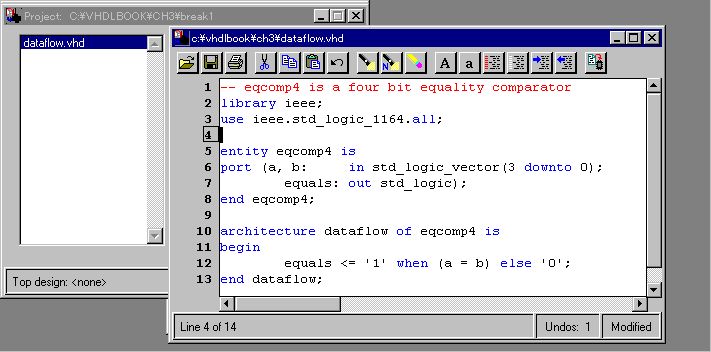

手順5 EditパネルでSelectedをクリックするとWarpのテキストエディタが開き、dataflow.vhdが自動的にロードされる(図2)。

図2 Warp2テキストエディタ

ここではファイルの中身の理解にはこだわらない。そのままsaveしないでcloseする。

手順6 SynthesisOptionパネルのSetTopをクリックすると左下のステータスバーにTop design dataflow.vhdと表示させる。

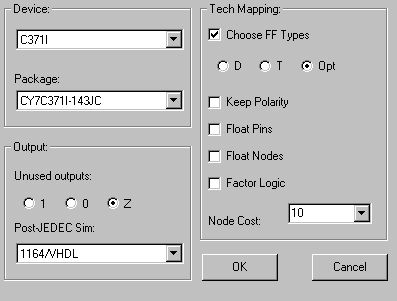

手順7 SynthesisOptionパネルのDeviceをクリックするとDeviceダイヤログが開く。スクロールリストからDeviceをc371iに選ぶなどして図3のように設定し、OKボタンを押す。

図3 Deviceダイヤログ

図3 Deviceダイヤログ 手順8 CompileパネルからSmartボタンをクリックする。コンパイルが実行され、1分程して完了するとコンパイレーション・ウインドウの左下にCompilation Successfulと表示される。確認後ウインドウを閉じる。

手順9 ToolメニューからNovaをクリックする。Warp2はVHDLシミュレータは持っていないが、代りにJEDECファイルをシミュレートするファンクション・シミュレータNovaを備えている。NovaでFileメニューからOpenを選んでdataflow.jedを開くとNovaシミュレーショ・ウインドウに数本のトレースが表示される。

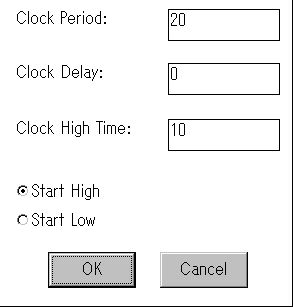

手順10 信号名a_0をクリックするとトレースが白からライトブルーに変り、a_0

信号が選択されたことを示す。EditメニューからClockを選ぶとダイアログボックス(図4)が開くので、OKを押してデフォルトを受け入れる。b_0にも同様のClock信号を割り当てる。以下a_1とb_1,a_2とb_2,a_3にも同様の操作を行う。

図4 Clockダイヤログ

図4 Clockダイヤログ手順11 信号b_3ではa_3と異なる信号を作る。b_3のトレースの上にカーソルを置き、マウスの左ボタンをクリックしたまま右にドラッグするとドラッグした範囲が白く変わる。適当はところでボタンを離すと選択された範囲がライトブルーに変わる。EditメニューからHighを選ぶとこの領域が'1'にセットされる。

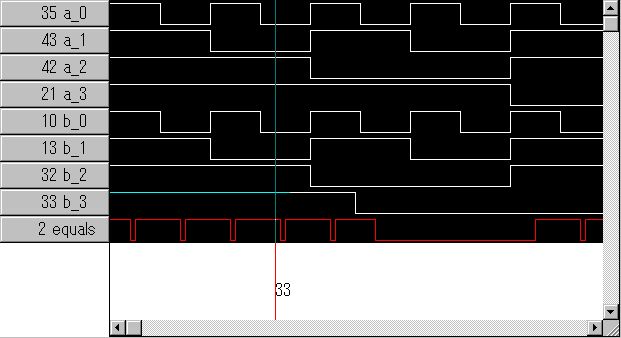

手順12 SimulateメニューからExcuteを選ぶと出力equalsのトレースが更新される(図5)。表示させる信号はViewメニューのEdit Viewオプションを用いて任意に選択できる。

図5 Novaシミュレータ

手順13 NovaのFileメニューからExitを選択。

手順14 GalaxyのProjectメニューからSaveを選択。

手順15 GalaxyをProjectメニューからQuitを選択し終了する。

VHDLの文法

あらゆるVHDL設計記述では、少なくとも一対のエンティティ(entity)/アーキテクチャ(archtecture)記述から構成される。エンティティ宣言は入力と出力のインタフェースを定義し、アーキテクチャー宣言はエンティティの実際の回路の機能を記述する。この他にオプションとしてpackage記述とconfiguration記述がある。package記述は使用頻度の高い宣言をパッケージにして退屈な繰り返し作業を軽減すると同時に設計の一貫性を確実なものにする。このようなテキスト記述によって、マイクロプロセッサのような複雑なものからNANDゲートのような簡単な論理回路まで実現できる。

注)VHDLテキスト中でーー(ダッシュ二つ)で始まる行はすべて注釈行と解釈される。

(1)エンティティ宣言

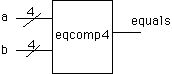

エンティティ宣言は、回路の外から見える入力と出力のインタフェース、つまりポートを記述する。回路図のブロック図とよく似ている。シミュレーションや論理合成を行う前に、あらゆる参照されたエンティティは対応するアーキテクチャに結合されなければならない。エンティティ宣言で提供される情報(名前、各ポートの方向、およびデータ型)には、その回路のポートを上位回路のポートに接続したり、シミュレーションでテストベンチの入力ステミュラスを開発するために必要なあらゆる情報が盛り込まれる。しかし、実際の回路の動作はこのエンティティ宣言には含まれていない。簡単な設計記述のエンティティ宣言の具体例をリスト1に示す。これは4ビットの一致回路(図6)を表したものである。

図6 4ビット一致回路ブロック図

entity eqcomp4 is

port(a,b: in bit_ vector(3 downto 0);

equals: out std_logic);

end eqcomp4;

リスト1 エンティティ宣言の例

エンティティ宣言は、名前(この例ではeqcomp4)とエンティティのすべての入力と出力を定義するポート文で構成される。このポートリストでは三つのポート、a,bとequalsが定義される。これら三つのポートのそれぞれは方向(この例ではin, out)とデータ・タイプ(この例では4ビットアレイを規定するbit_vector(3 downto 0)と単一のビット値を表すstd_logic)が与えられる。

(2)アーキテクチャ本体

最小のVHDLソースファイルの第二の部分はアーキテクチャ本体である。設計で参照されるあらゆるエンティティ宣言は少なくとも一対の対応するアーキテクチャ本体を伴ったものでなければならない。この宣言でポートと内部回路が対応付けられる。リスト2に、先に示したエンティティ宣言と対をなすコンパレータ回路のアーキテクチャ本体を示す。

architecture dataflow of eqcomp4 is

begin

equals <= '1' when (a = b) else '0';

end dataflow;

リスト2 アーキテクチャ宣言の例

アーキテクチャ宣言は唯一の名前であるアーキテクチャ名(この例ではdataflow)で始まり、アーキテクチャが結合されるエンティティの名前(この例ではeqcomp4)がその後に続く。アーキテクチャ名は一般に任意だが、behavior、dataflow、bool、rtl、structure、simなどが良く用いられる。

beginとendのキーワードで挟まれたアーキテクチャ宣言の中に、実際のceqcomp4の機能(ビヘイビア)記述が指定される。endの後のアーキテクチャ名は省略して単にend;と記述することも可能である。

VHDLで組み合わせ論理回路を記述する型は一通りではない。この簡単な設計記述(リスト2)はaとbが等しいときに出力(equals)に'1'の値が、異なるときに'0'の値が代入されることを指示する。このたった一行の同時記述はVHDLの最も簡単な書式の例を示しているが、VHDLでは違った型の多くの同時記述が利用可能である。基本的な設計記述スタイルは抽象性の高い順に機能(Behavior)記述、データフロー(Dataflow)記述、構造(Structure)記述などである。

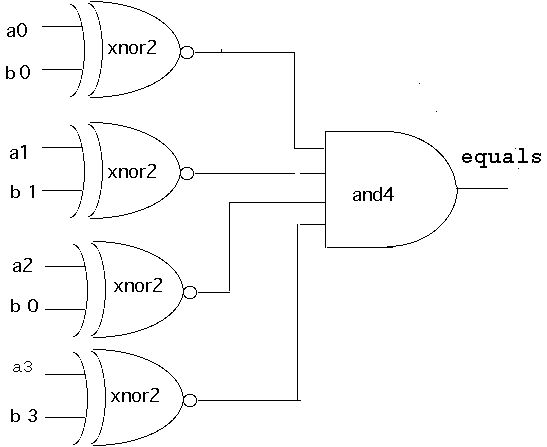

図6で示した一致回路はゲートで構成すると図7のように書き表せる。

図7 4ビット一致回路(ゲート構成)

これを構造記述で表したものがリスト3である。階層構造をなしている下位のxnor2やand4はpackage記述によりgatespkgというライブラリに収められている。

library ieee;

use ieee.std_logic_1164.all;

entity eqcomp4 is port(

a, b: in std_logic_vector(3 downto 0);

equals: out std_logic);

end eqcomp4;

architecture structure of eqcomp4 is

use work.gatespkg.all;

signal x : std_logic_vector( 3 downto 0);

begin

uo:xnor2 port map (a(0), b(0),x(0));

u1:xnor2 port map (a(1), b(1),x(1));

u2:xnor2 port map (a(2), b(2),x(2));

u3:xnor2 port map (a(3), b(3),x(3));

u4:and4 port map (x(0),x(1),x(2),x(3), equals);

end structure;

リスト3 一致回路の構造記述

(つづく)

参考文献

1.「VHDLによるロジック設計入門」トランジスタ技術、1997年12月号特集

2.「パソコン用VHDLシミュレータの登場」CQ出版、Design Wave Magazine No.2

2.Warp User's Guide, Release 4.2, Cypress Semiconductor Inc.,1997.

3.Warp Refference Manual, Release 4.2, Cypress Semiconductor Inc.,1997.

4. David Pellerin・Douglas Taylor "VHDL Made Easy!" (Prentice Hall,1997)

5.Kevin Skahill "VHDL for programmable logic" (Addison-Wesley,1996)

図面

図1 New Projectダイヤログ

図2 Warp2テキストエディタ

図3 Deviceダイヤログ

図4 Clockダイヤログ

図5 Novaシミュレータ

図6 4ビット一致回路ブロック図

図7 4ビット一致回路(ゲート構成)